Kou-Hsing Cheng1 and Shun-Wen Cheng This email address is being protected from spambots. You need JavaScript enabled to view it.2 1Department of Electrical Engineering, National Central University Taoyuan, Taiwan 320, R.O.C.

2Department of Electrical Engineering, Tamkang University Tamsui, Taiwan 251, R.O.C.

Received:

January 6, 2005

Accepted:

March 11, 2005

Publication Date:

June 1, 2005

Download Citation:

||https://doi.org/10.6180/jase.2005.8.2.08

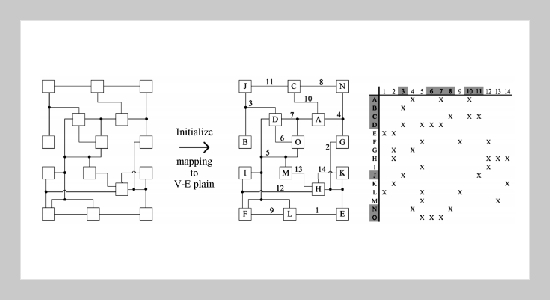

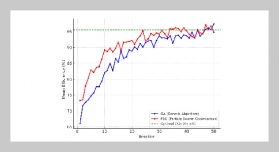

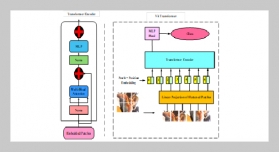

This work presents two approaches with a high probability of obtaining maximal and minimal connection in an electrical network. The first method, referred to herein as Edge-Node Interleaved Sort for Leaching and Envelop (ENISLE) algorithm, uses both node information and edge information and works effectively on a common network. The second method, referred to herein as Interleaved Cutting-ENISLE (IC-ENISLE) algorithm, uses node and edge information as well as the max-min dual property. This method works better than ENISLE in an electrical circuit. This study also finds the relationship between minimal connection and the initial node-edge pairs distributed condition/entropy on hypergraph circuit. Under a nearly max-connection reservation, a circuit with a high initial potential/entropy implies a high probability of aiming the minimal connection. From our approach, the work indicates that the minimum connection plane characteristics significantly affect the connection problems. Our results further demonstrate that, with respect to the sequential circuit or other time-sensitive circuits as an indivisible element, record the level is even or odd, and/or record the level number of every node or edge, are highly effective for modern circuit network connection.ABSTRACT

Keywords:

ENISLE, Minimal-connection, Quasi-random, Clustering Effect, Radix Sort, Hypergraph, VLSI Circuit

REFERENCES