REFERENCES

- [1]Keating, M. and Bricaud, P.: ‘Reuse Methodology Manual for System-on-Chip Designs’ , Kluwer Academic Publishers, 1998

- [2]IEEE P1500 Web Site, http://grouper.ieee.org/groups/1500/

- [3]Zorian, Y., Marinissen, E.J. and Dey, S.: ‘Testing Embedded-Core Based System Chips’ , In proceedings IEEE International Test Conference, pp. 130-134, Oct. 1998

- [4]Aerts, J. and Marinissen, E.J.: ‘Scan Chain Design for Test Time Reduction in Core-Based ICs’ , In Proceedings IEEE International Test Conference, pp. 448-457, Oct. 1998

- [5]Varma, P. and Bhatia, S.: ‘A Structured Test Re-Use Methodology for Core-Based System Chips’ , In Proceedings IEEE International Test Conference, pp. 294-302, Washington, DC, Oct. 1998

- [6]Marinissen, E.J., Arendsen, R., Bos, G., Dingemanse, H., Lousberg, M. and Wouters, C.: ‘A Structured and Scalable Mechanism for Test Access to Embedded Reusable Cores’ , In Proceedings IEEE International Test Conference, pp. 284-293, Oct. 1998

- [7]Zorian,Y.: ‘A Distributed BIST Control Scheme for Complex VLSI Devices’ , In Proceedings IEEE VLSI Test Symposium, pp. 6-11, April. 1993

- [8]Bleeker, H., van den Dijnden, P. and de Jong, F.: ‘BoundaryScan Test-A Practical Approach. Kluwer Academic Publishers’ , Dordrecht, Netherlands, 1993

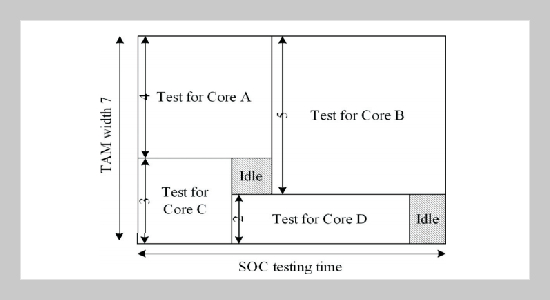

- [9]Iyengar, V., Chakrabarty, K. and Marinissen, E.J.: ‘On Using Rectangle Packing for SOC Wrapper/TAM Co-Optimization’ , In Proceedings IEEE VLSI Test Symposium, pp. 253-258., April. 2002

- [10]Iyengar, V., Chakrabarty, K. and Marinissen, E.J.: ‘Test wrapper and test access mechanism co-optimization for system-on-chip’ , In Proceedings IEEE Internal Test Conference, pp.1023-1032, Oct. 2002

- [11]Iyegnar, V., Chakrabarty, K. and Marinissen, E. J.: ‘Test Access Mechanism Optimization, Test Scheduling, and Tester Data Volume Reduction for System-on-Chip’ , In Proceedings IEEE Transaction on Computers, pp. 1619-1631, Dec. 2003

- [12]Goel, S. K. and Marinissen, E.J.: ‘Effective and Efficient Test Architecture Design for SOCs’ , In Proceedings IEEE International Test Conference, pp. 529-538, Oct. 2002

- [13]Larrson, E. and Peng, Z.: ‘An Integrated framework for the Design and Optimization of SOC Test Solution’ , In Proceedings Date, Automation and Test in Europe Conference and Exhibition 2001, pp.138-144, March. 2001

- [14]Sehgal, A. and Chakrabarty, K.: ‘Efficient Modular Testing of SOCs Using Dual-Speed TAM Architectures’ , In Proceedings Date, Automation and Test in Europe Conference and Exhibition, pp. 422-427, Feb. 2004

- [15]Xu, Q. and Nicolici, N.: ‘Multi-frequency Test Access Mechanism design for Modular SOC Testing’ , In Proceedings 13th Asian Test Symposium, pp. 2-7, Nov. 2004

- [16]Chakrabarty, K., Iyengar, V. and Krasniewski, M.D.: ‘Test Planning for Modular Testing of Hierarchical SOCs’ , In Proceedings IEEE Transactions on Computer-Aided Design of integrated Circuits and Systems, pp. 435-448, March, 2005

- [17]Chakrabarty, K., Iyengar, V., Krasniewski, M.D. and Kumar, G.N.: ‘Design and Optimization of Multi-level TAM Architectures for Hierarchical SOCs’ , In Proceedings 21st VLSI Test Symposium, pp. 299-304, April. 2003

- [18]Sehgal, A., Chakrabarty, K. and Iyengar, V.: ‘SOC Test Planning Using Virtual Test Access Architectures’ , In Proceedings IEEE Transactions on Very Large Scale Integration Systems, pp. 1263-1276, Dec. 2004

- [19]Sehgal, A., Chakrabarty, K., Iyengar, V. and Krasniewski, M.D.: ‘Test Cost Reduction for SOCs Using Virtual TAMs and Lagrange Multipliers’ , In Proceedings Design Automation Conference, pp. 738-743, June. 2003

- [20]Goel, K. and Marinissen, E.J., “Cluster-based Test Architecture Design for System-on-Chip,” In Proceedings IEEE VLSI Test Symposium (VTS), 2002, pp. 259-264.

- [21]Goel, K. and Marinissen, E.J., “A Test Time Reduction Algorithm for Test Architecture Design for Core-Based System Chips,” Journal of Electronic Testing: Theory and Applications, 2003, pp. 425-435.