Jen-Shiun Chiang This email address is being protected from spambots. You need JavaScript enabled to view it.1, Teng-Hung Chang1 and Pou-Chu Chou1 1

Received:

June 22, 2001

Accepted:

July 27, 2001

Publication Date:

September 1, 2001

Download Citation:

||https://doi.org/10.6180/jase.2001.4.3.02

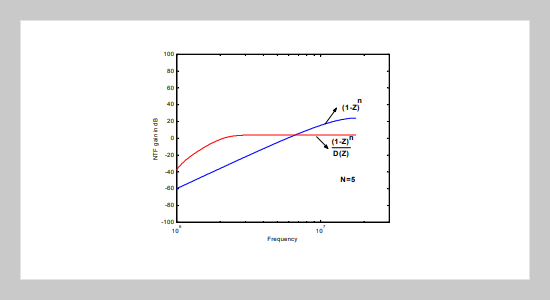

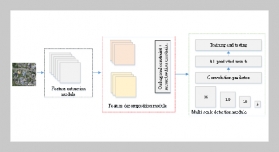

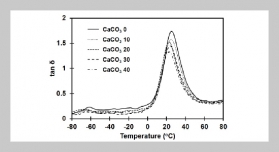

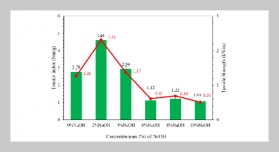

A new sigma-delta modulator architecture for wide bandwidth application called cascaded feedforward sigma-delta modulator is proposed in this paper. This sigma-delta modulator is similar to the conventional feedforward summation sigma-delta modulator. The conventional feedforward summation sigma-delta modulator uses multi-bit feedback and therefore a multi-bit digital-to-analog converter (DAC) is needed. Due to the nonlinearity of the multi-bit DAC, it is difficult to be implemented. On the other hand the proposed approach uses 1.5-bit feedback, and thus the implementation of the analog part is much easier than the conventional one. Since the 1.5-bit feedback will cause coarse quantization errors, error cancellation must be done in the digital part. Here an adaptive filter with least mean square algorithm is used to reduce the nonlinear effect. The simulation results show that the signal to noise plus distortion ratio (SNDR) of this architecture is very close to that of the ideal feedforward summation sigma-delta modulator with multi-bit DAC and can be used for the wide bandwidth application.ABSTRACT

Keywords:

Wide-bandwidth, Cascaded Sigma-delta Modulator, Feedforward, xDSL, Dual-quantizer

REFERENCES